Popis výrazů, se kterými pracuje obor číslicová technika.

Momentální třídění: Podle data vytvoření (vzestupně) Třídit chronologicky: Podle poslední aktualizace | Podle data vytvoření

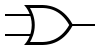

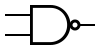

Negace logického součtu:

Česky bychom řekli, že výstup Y je, pokud není přítomen signál na vstupu A nebo vstupu B nebo na obou vstupech současně. Negace logického součinu - NOR | |||||||||||||||||||

|

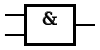

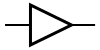

Logický součin:ANDTento člen provádí funkci tzv. logického součinu (konjunkce).

Česky bychom řekli - vstup A a vstup B, nebo vstup A i vstup B musí být přítomen, aby byl také výstup. | |||||||||||||||||||

|

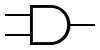

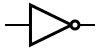

Logický součet:ANDTento člen provádí funkci tzv. logického součinu (konjunkce).

Česky bychom řekli, že pokud má hodnotu vstup A nebo vstup B, je výstup aktivní. Logický součet | |||||||||||||||||||

|

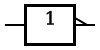

Zpožďovací člen - Buffer:Nejjednodušším logickým členem je buffer neboli zpožďovací člen, který realizuje funkci identity.

| ||||||||||

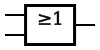

Negace logického součinu:Tento člen provádí funkci tzv. negovaného logického součinu. Je to nejběžněji používané hradlo. Propojením vstupů je schopno pracovat jako invertor. Lze pomocí něho realizovat většinu klopných obvodů.

Česky bychom řekli, že výstup Y je, pokud není přítomen signál na obou vstupech A a B současně. | |||||||||||||||||||

|

Pravidlo asociativní:Platí, že: A(B . C) = (A . B)C nebo A+(B + C) = (A + B) + C | |

|

Pravidlo komutativní:A . B = B . A nebo také: A + B = B + A | |

|

Pravidlo distributivní:A . B + A . C = A(B + C) nebo také (A + B).(A + C) = A + B . C | |

|

Pravidlo vyloučení třetího:

nebo  | |

|

Dokumentace k této stránce

Dokumentace k této stránce